# Towards Dependable CPS/IoT Ecosystems

### DISSERTATION

zur Erlangung des akademischen Grades

### Doktor der Technischen Wissenschaften

eingereicht von

Dipl.-Ing. Haris Isakovic

Matrikelnummer 00325697

an der Fakultät für Informatik

der Technischen Universität Wien

Betreuung: Univ.Prof. Radu Grosu Zweitbetreuung: Univ.-Prof. Ezio Bartocci

Diese Dissertation haben begutachtet:

Univ.Prof. Jerker Delsing

Univ.Prof. Manuel Wimmer

Wien, 3. August 2021

Haris Isakovic

# Towards Dependable CPS/IoT Ecosystems

### DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

### Doktor der Technischen Wissenschaften

by

**Dipl.-Ing. Haris Isakovic** Registration Number 00325697

to the Faculty of Informatics

at the TU Wien

Advisor: Univ.Prof. Radu Grosu Second advisor: Univ.-Prof. Ezio Bartocci

The dissertation has been reviewed by:

Univ.Prof. Jerker Delsing

Univ.Prof. Manuel Wimmer

Vienna, 3<sup>rd</sup> August, 2021

Haris Isakovic

## Erklärung zur Verfassung der Arbeit

Dipl.-Ing. Haris Isakovic

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 3. August 2021

Haris Isakovic

### Acknowledgements

I would like to express my deepest gratitude to professor Radu Grosu for his support and mentorship during my PhD study. He inspired us to new heights and to reach the best in us both in our professional and personal lives. Further, I owe a big thank you to professors Ezio Bartocci and Peter Puschner for their cooperation and valuable advice. To my colleagues Christian, Armin, Oliver, Bernhard, Denise, and Ramin, thank you very much. You helped me numerous times, you have been there for me not only as colleagues but as dear friends. In the uncharted sea of projects I managed to find my way with selfless help of our secretaries Maria, Gerda and Viktoria.

I am thankful to all my friends and colleagues from projects EMC2, Productive4.0, CPS/IoT Ecosystem, ACROSS, MultiPartes, iDev4.0 and Adeptness. They shared with me their unreserved dedication, utmost professionalism, creative insights, unmatched expertise and those valuable moments of sincere friendship.

This thesis was a long process, and I am proud to say that I always had friends to rely upon. Through all my ups and downs, they never showed any doubt in my abilities and they gave me some of the best moments in my life.

I cannot express how fortunate I feel to have such a wonderful family behind me, from my sister Nerma, her husband Nedim, all aunts, uncles, cousins, to my late grandparents. I feel an incredible sense of respect for all they did for me on this journey, I hope I get the chance to return the favor soon.

My wife Azemina is the person who carried much of the burden with me, she is my fortress of solitude, my rock, and my safe harbor. This is the person who loved me from the first day we met, and never showed anything but relentless pursuit of support and respect. She pushed me when I felt giving up, and she lifted me up when I felt down. She gave me the biggest joy in my life, our daughter Nora. Together, they make every day in my life wonderful.

Two people without whom this would be unimaginable are my parents Enisa and Šefik. I dedicate this work to them because it is their unreserved sacrifice that allowed me to be here. They motivated and guided me my whole life, to reach this goal. Without a grain of doubt, thorough sickness and all the hardships, they kept giving even when their help was no longer needed. I will forever be grateful for all they did to make this possible.

### Kurzfassung

Wir befinden uns am Anfang einer technologischen und sozioökonomischen Revolution, in der Computerintelligenz Teil gewöhnlicher physischer Objekte wird, soziale Interaktionen regelt und die menschliche Kognition im Allgemeinen beeinflusst. Wir betreten die Ära der Smart World! Intelligente Geräte werden zu integralen Bestandteilen industrieller Systeme, von Transport, Gesundheitswesen, Bauwesen, Chemie, Energie, Bildung und Unterhaltung. Wir stehen vor einer rasanten Zunahme vernetzter Rechenknoten im gesamten Spektrum industrieller Anwendungen und Allzweckanwendungen.

Der technologische Träger dieser Revolution ist die Synergie zwischen Cyber-Physischen Systemen (CPS) und dem Internet der Dinge (IoT). Diese beiden Konzepte spezifizieren Fähigkeiten von rechnergestützten Systemen, die physikalische Welt mithilfe von mathematischen Modellen zu interpretieren, die physikalische Umgebung zu beobachten und zu manipulieren sowie Informationen über verschiedene Einsatzbereiche hinweg zu kommunizieren.

In dieser Arbeit definieren wir das Konzept des CPS/IoT-Ökosystems als eine hierarchische Struktur, die Praktiken und Verfahren für die Modellierung, das Design, die Entwicklung, die Ausführung und den Betrieb von intelligenten Systemen regelt. Wir unterteilen diese Systeme in drei lose voneinander abhängige Betriebsbereiche: die Cloud, den Fog und den Swarm.

Weiter, wir schlagen eine Sammlung von Methoden und Ansätzen vor, die ein zuverlässiges Design, eine zuverlässige Ausführung und einen zuverlässigen Betrieb von CPS/IoT-Ökosystemen ermöglichen. Insbesondere beginnen wir mit Methoden zur Gewährleistung der deterministischen Ausführung von Aufgaben in sicherheitsrelevanten Anwendungen. Als Erweiterung dieser Notiz schlagen wir eine Virtualisierungstechnik für Kommunikationskanäle für Many-Core-Plattformen mit begrenzten physikalischen Schnittstellen und eine sichere Kommunikationsarchitektur vor, die auf integrierten Architektureigenschaften wie der zeitlichen und räumlichen Isolierung von Knoten beruht.

Das CPS/IoT-Ökosystem ist eine sehr heterogene Umgebung mit Hardware- und Softwarekomponenten, die von mehreren Organisationen entwickelt und implementiert werden. Um die Kohärenz zwischen verschiedenen Komponenten zu gewährleisten und die Komplexität zu reduzieren, schlagen wir ein kontinuierliches Integrations- und Bereitstellungsschema (CI/CD) für das CPS/IoT-Ökosystem vor. Darüber hinaus demonstrieren wir einen Runtime Verification (RV) Mechanismus, der die Grundlage für die Orchestrierung der Dienstgüte (QoS) und die dynamische Rekonfiguration von CPS/IoT-Anwendungen bildet.

Am Ende schlagen wir Methoden vor, um ein energetisch nachhaltiges CPS/IoT-Ökosystem zu erreichen. Darüber hinaus haben wir ein Modell zur Vorhersage des Energieverbrauchs im gesamten CPS/IoT-Spektrum mit Rückblick auf die Smart-World-Revolution definiert. Um den durch smarte Geräte verursachten Energie-Overhead zu reduzieren, schlagen wir eine alternative Stromversorgungsmethode für CPS/IoT-Sensorknoten vor.

### Abstract

We find ourselves at the beginning of a technological and socio-economic revolution, where computational intelligence is becoming part of ordinary physical objects, governing social interactions and affecting human cognition in general. We are entering the era of a Smart World! Smart devices are becoming integral parts of industrial systems, from transportation, healthcare, construction, chemical, energy, education and entertainment. We are facing a rapid increase of networked-computing nodes across the spectrum of industrial applications and of general-purpose applications.

The technological carrier of this revolution is the synergy between cyber-physical systems (CPS) and the Internet of Things (IoT). They specify the abilities that computational systems need to possess, in order to interpret their physical world by using mathematical models, to observe and manipulate their physical environment through sensors and actuators, and to communicate information across different scopes of operation.

In this thesis we define the concept of CPS/IoT Ecosystem as a hierarchical structure, that governs practices and procedures for modeling, design, development, execution and operation of smart systems. We divide these systems in three loosely dependent scopes of operation: the cloud, the fog, and the swarm.

Furthermore, we propose a series of methods and approaches that support the dependable design, execution, and operation of CPS/IoT Ecosystems. In particular, we start with methods ensuring the deterministic execution of tasks in safety constrained applications. As an extension to these methods we propose a virtualization technique for communication channels for many-core platforms with limited physical interfaces, and a secure communication architecture that relies on integrated architectural properties such as temporal and spatial isolation of nodes.

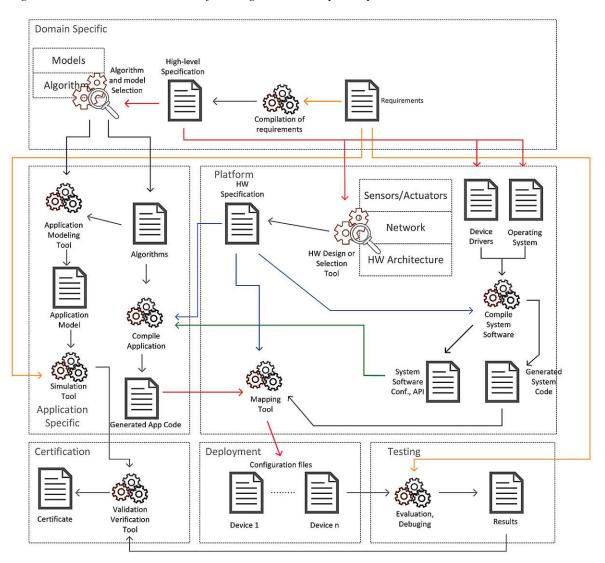

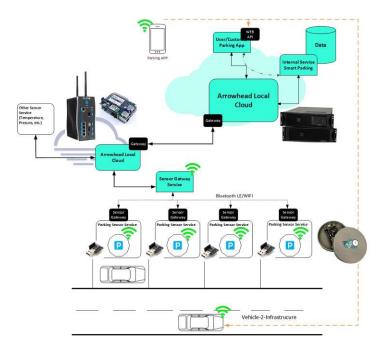

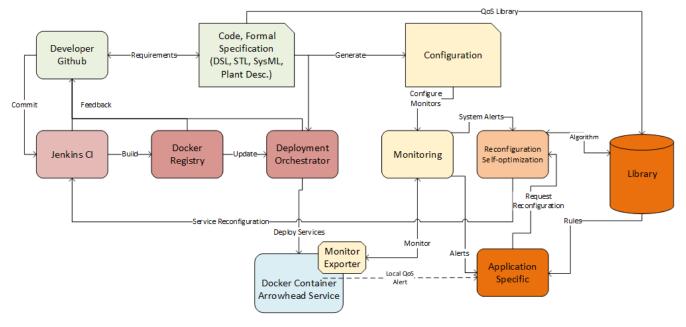

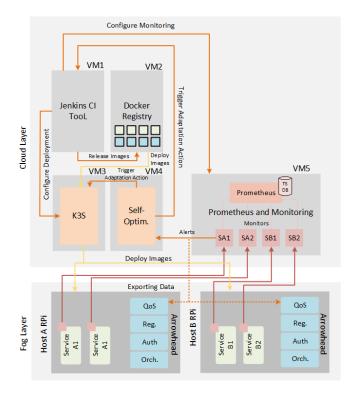

A CPS/IoT Ecosystem is a highly heterogeneous environment with hardware and software components that are designed and implemented by multiple organizations. To ensure coherence between different components and to reduce complexity we propose a continuous integration and deployment (CI/CD) scheme for CPS/IoT Ecosystem. Furthermore, we demonstrate a runtime verification (RV) mechanism that provides a basis for quality of service (QoS) orchestration and dynamic reconfiguration of CPS/IoT applications.

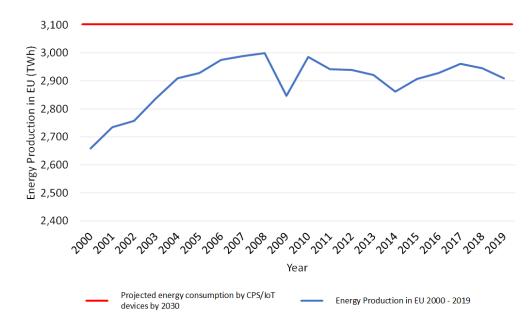

As final step in this thesis we propose methods to achieve energy-sustainable CPS/IoT Ecosystems. Moreover, we defined a model to predict energy consumption across the

CPS/IoT spectrum with retrospect to the Smart-World revolution. To reduce energy overhead created by smart devices we propose an alternative energy consumption method for CPS/IoT sensor nodes.

In conclusion, this thesis tries to seed methodological guidelines on how to build dependable CPS/IoT Ecosystems for applications with various confidence requirements. We want to understand the upcoming changes and reduce eventual effects of ad-hoc development. To explain physical environments using mathematical models and to learn new emerging behaviors using this massive incursion of new data and new insights.

## Contents

| K        | urzfassung                                                                                                                           | ix           |

|----------|--------------------------------------------------------------------------------------------------------------------------------------|--------------|

| A        | bstract                                                                                                                              | xi           |

| C        | ontents                                                                                                                              | xiii         |

| 1        | Introduction         1.1       Motivation                                                                                            | <b>3</b>     |

|          | 1.2Problem Statement and Research Gap1.3Aim of the Thesis1.4Publications                                                             |              |

|          | 1.5 Methodology $\ldots$                                                                                                             | 13           |

|          | 1.6       Thesis Synopsis         1.7       Summary of the Thesis         1.8       Contributions of the Thesis                      | . 31         |

|          | 1.8       Contributions of the Thesis                                                                                                | 45           |

|          | 1.10       Conclusion                                                                                                                | . 47<br>. 49 |

| <b>2</b> | Virtual CAN Lines in an Integrated MPSoC Architecture                                                                                | 57           |

| 3        | Secure Channels in an Integrated MPSoC Architecture                                                                                  | 67           |

| 4        | A heterogeneous time-triggered architecture on a hybrid system-on-<br>a-chip platform                                                | 75           |

| 5        | A Mixed-Criticality Integration in Cyber-Physical Systems: A Het-<br>erogeneous Time-Triggered Architecture on a Hybrid SoC Platform | 83           |

| 6        | CPS/IoT Ecosystem: A Platform for Research and Education                                                                             | 113          |

| 7        | QoS for Dynamic Deployment of IoT Service                                                                                            | 123          |

| 8        | An Energy Sustainable CPS/IoT Ecosystem                                                                                              | 133          |

|          |                                                                                                                                      | xiii         |

| List of Figures    | 153 |

|--------------------|-----|

| List of Tables     | 153 |

| List of Algorithms | 155 |

### Preface

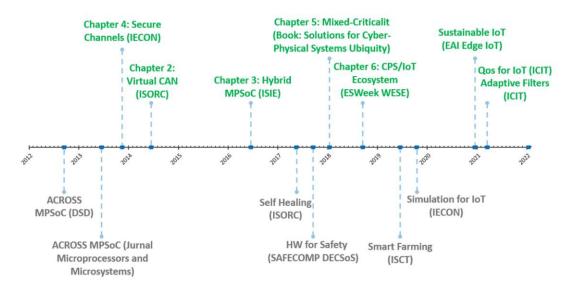

The purpose of this cumulative doctoral thesis is to motivate and summarize the research work I have undertaken as PhD student at the CPS division of the faculty of informatics, TU Wien. During this time, my work took place within several CPS/IoT research projects, and it resulted in thirteen publications.

This thesis unifies all the individual research activities as a concerted work, that explores how to build dependable systems within a CPS/IoT Ecosystem, and which shows how to achieve this goal by using a structural hierarchy of computational systems. In short, the individual topics explored in our published work, advance the design, development, and operation of dependable CPS/IoT Ecosystems.

The thesis is constructed from two parts: 1) An introductory chapter that explains the motivation and methodology behind the topic of dependable CPS/IoT Ecosystems, and, 2) The relevant publications sorted as chapters in the thesis. Individual works were originally motivated and performed by different ideas and requirements. However, with this work we want to highlight how they fit in a larger picture and how they contribute to the holistic concept of a dependable CPS/IoT Ecosystem.

The diversity of topics, methods, and tools involved in this work is compelling. We want both to introduce the readers to the important aspects of each publication, and to establish an understanding of how these concepts contribute to the idea of a dependable CPS/IoT Ecosystem. For this purpose, we devised a side-note method, which is created from three types of notes, denoted by the questions Why?, What? and How?

Why? This note describes a motivational aspect of a subject, and it reminds the reader of the importance behind the statement, paragraph, or section towards greater good.

What? Each of these notes identifies a requirement to be fulfilled by the CPS/IoT Ecosystem or a challenge to be solved in order to establish a premise, or answer a question on the necessary steps towards a solution.

**How?** These notes will identify concrete solutions for the problems and remind users how these solutions correspond to given research questions.

### CHAPTER

### Introduction

#### 1.1 Motivation

Advances in science and technology in the last few decades have resulted in tremendously complex systems that extend over different disciplines, physical and temporal scales, and involve various individuals or organizations.

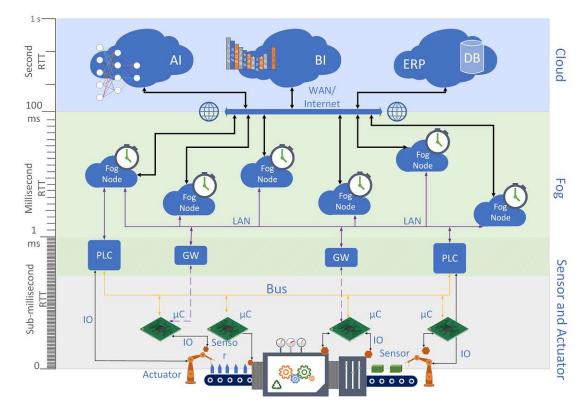

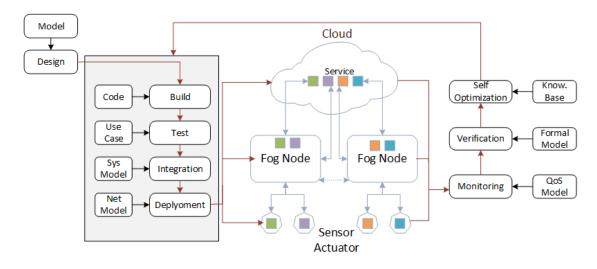

This thesis explores how cyber-physical systems are entangled within a complex web of the physical environment, the Internet, and the ability to maintain specific safety and security criteria. We define a CPS/IoT Ecosystem as a heterogeneous structure of hardware devices and corresponding software components distributed over three intertwined scopes of operation: the swarm, the fog, and the cloud (see Figure 1.1) [66].

CPS/IoT Ecosystems can be seen as a result of natural evolution, similar to the one that happened for biological systems, where single cells merged over time into tissues/organs/bodies to perform more complex tasks. The swarm of sensors/actuators, akin to the human skin/muscle cells, produces the big (real-time) data through its sensors, and consumes it with its actuators. This data is shared with the fog. The fog, akin to the spinal cord, controls the sensors and the actuators in real time. It is capable of doing mid-scale computational tasks and storing intermediate and temporary data for purposes of aggregation or filtering. The cloud, akin to the human brain, possesses theoretically unlimited storage and computation resources. It is here where the data is stored and where planning and other offline tasks such as machine learning mainly happen.

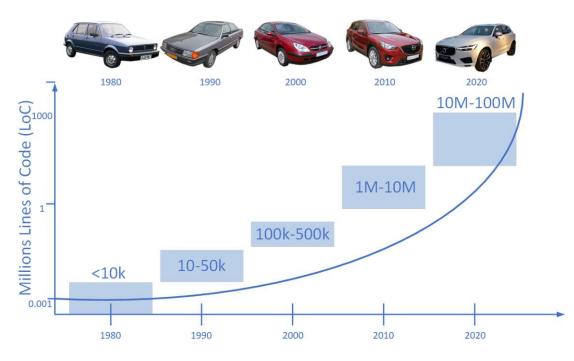

By combining these individual scopes of operation we can increase the capability of the system by a large margin, yielding new emerging functions and enabling new use cases. These new features create new opportunities but also increase overall complexity. A perfect example for this can be found in the automotive industry. The complexity of automotive software has increased exponentially over the past 40 years (see Figure 1.2). As the systems get more complex and more conservative in terms of dependability,

Figure 1.1: The architecture of a CPS/IoT Ecosystem. (Right) Three scopes of operation Cloud, Fog (Edge), Swarm (Sensors/Actuators). (Left) Time scale for the message exchange and reaction. Abbreviations: Artificial Intelligence (AI). Business Intelligence (BI). Enterprise Resource Planning (ERP). Data-Base (DB). Wide Area Network (WAN). Local Area Network (LAN). Programmable Logic Array (PLC). Communication Gateway (GW). Micro-controller ( $\mu C$ ). Input-Output (IO). Round-Trip Time (RTT).

these tasks are getting more difficult. The higher-dependability standards are essential as we wander from general-purpose applications towards industrial safety-constrained applications, such as car-2-infrastructure or industrial control.

Why are these new technologies necessary in already functional systems? We can look at this from two perspectives: Functional and Economical. In automotive industry, for example, these new features significantly improve the cars in terms of safety, convenience, and comfort. Generally, the functional motivation for this revolution can be summarized in the following statements: a) Increase general functionality and capabilities of a system, b) Increase system efficiency, c) Achieve emergent insights into a system.

If we observe this change from an economic perspective, this revolution creates brand-new markets, innovation in business models, reduces efforts and overheads, and enables a tighter bond between management and the field level of operation. For example, using a continuous integration and delivery methods can save up to 78% of development costs

4

[58]. By applying advanced machine learning methods on sensor data collected from the physical environment of a machine it is possible to improve failure detection of robust mechanical systems by a significant margin, thus reducing maintenance and eventual downtime costs [57].

To conclude, the rise in complexity is inevitably advancing, and it is arguably justified. This raises the question: "How can we maintain the dependability of these systems despite the increase in complexity?" This thesis proposes a series of technologies that support the development of some of the missing pieces in the CPS/IoT puzzle.

Figure 1.2: Software complexity in automotive sector, in terms of lines of code (LoC).

**Why?** A Smart World will require an enormous number of devices over next decade. An ad-hoc implementation of the smart world could potentially lead to chaos. It could result in an incomprehensible complexity, one which could endanger safety-critical industrial systems, economic institutions, and personal privacy.

#### 1.2 Problem Statement and Research Gap

The three scopes of operation within a CPS/IoT Ecosystem, are fully capable of operating individually. In fact they have been observed and explored as separate entities in the past. However, with an increasing ability to analyze and understand our physical environment, new methods for developing efficient CPS are emerging. A necessary requirement for this new paradigm is constant communication, both horizontally and vertically. Horizontal

communication happens within a scope of operation, among components or devices, through a bus or LAN. As a vertical hierarchy, a CPS/IoT Ecosystem establishes a functionally relevant vertical communication, from the tiniest device to the Cloud.

The design and development process for each scope of operation is different from the others; they are loosely integrated, with numerous gaps in-between. This work explores the ability of these systems to facilitate dependability, both as an assembly of its defining properties, and also through a perspective of individual properties.

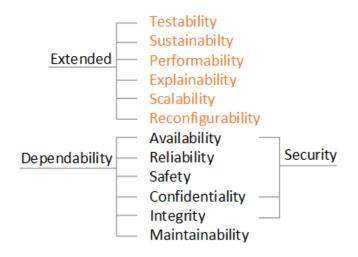

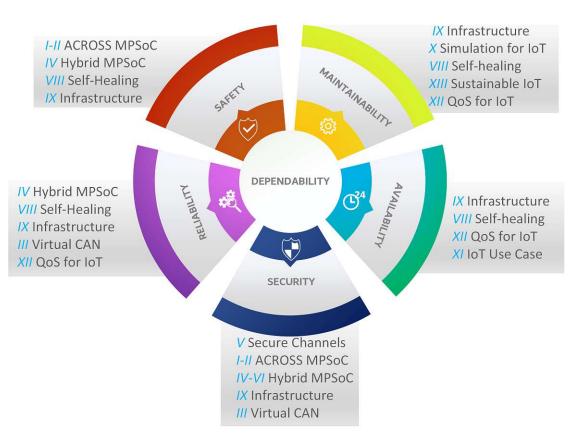

The dependability of computing systems was initially defined either as "the ability to deliver service that can justifiably be trusted" or as "the ability to avoid service failures that are more frequent and more severe than is acceptable" [28]. It is commonly accepted that the dependability of a computing system is determined by six attributes: availability, reliability, safety, integrity, and maintainability [28]. The availability attribute can be described as a readiness of the system to deliver correct service. The reliability attribute is a probabilistic measure of the system's ability to deliver correct service in a certain period of time. The safety attribute is augmenting reliability in terms of avoiding catastrophic failures that could result in a loss of a life, environmental or economic damages. Integrity is an attribute that guarantees that a system is not improperly or maliciously altered. Finally, the ability of a system to be properly repaired or modified in its life-cycle is referred to as maintainability.

More recent definitions of dependability include security as an attribute that comprises integrity and confidentiality [70][28]. This means that dependability and security largely overlap, and in the extension of the text we will assume dependability encompasses security.

Examples for dependable systems are traditionally drawn from industries with a strong safety, economic or environmental impact in case of catastrophic failure, such as aerospace, avionics, railway or automotive [49]. However, in recent years the scopes of operations of these systems have expanded into other domains, such as updates over the internet, multimedia, and communication with civil infrastructure.

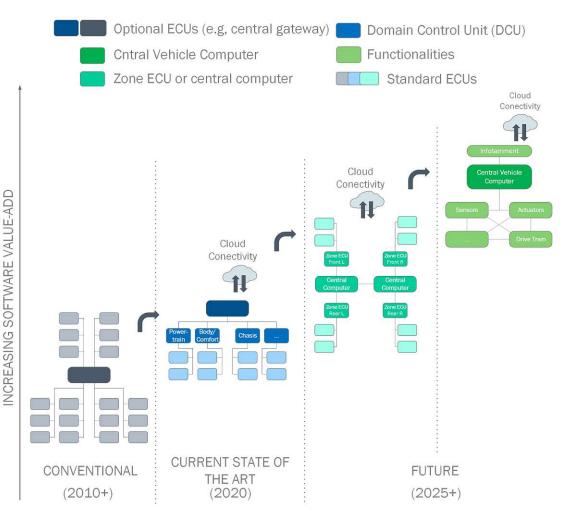

Automotive vehicles are increasingly linked with cloud servers over the Internet. They

Figure 1.3: Dependability attributes.

perform tasks such as monitoring, multimedia streaming, and even over the air updates [78]. Figure 1.4 shows the gradual evolution of on-board architectures in the automotive sector, and the importance of connectivity with the Internet and infrastructure. Another

Figure 1.4: Evolution of on-board architectures in the automotive sector [44].

example is the industrial Internet-of-Things (IoT), where entire industrial processes are interlinked over multiple scopes of operation [46].

In hindsight, the dependability definition can be further extended to include attributes such as performability [84], sustainability [39], testability [84], explainability [40], scalability [72] and reconfigurability [86]. One common conclusion is that these attributes address issues that emerge as a result of overuse or extended usage time, interconnection with other systems, or application in environmentally sensitive settings. The dependability of computing systems needs to be adapting to emerging behaviors and system structures (e.g., IoT, quantum computing). With this in mind, we would like to revisit dependability considerations, standardization, and best practices in the domain of CPS/IoT Ecosystem.

As defined in Section 1.1 of the document we assume that a CPS/IoT Ecosystem (see Figure 1.1) can be divided in three hierarchical scopes of operation: the cloud, the fog,

and the swarm. Each individual system within this hierarchy is defined by a set of different structural, resource, and functional properties. Their purpose and application will determine the required level of dependability or standard conformity that needs to be achieved. For example, the same functionality can be achieved with multiple devices, but only certain devices are certified for a certain level of dependability or security.

Further, a CPS/IoT Ecosystem is determined by its intended function, and that is to establish a reliable connection to the physical environment, collect data, analyze it, and learn emerging behaviors that can be used to increase efficiency or ensure entirely new functions of a certain system. On the other hand, this increases the overall risk of emerging faults, errors, and failures.

The level of co-dependency of individual components yields new emerging behaviors that are often not considered in the design of the individual components and their failure model. Thus, when we explore dependability we need to consider how actions of individual components resonate on the global scale of a CPS/IoT Ecosystem. Linking systems such as vehicles to the Internet increases security risks that can have a significant impact on the safety and dependability of the system in general [37].

In conclusion, we would like to highlight challenges that are developing with the evolution of computational systems in terms of dependability:

- Categorize dependability requirements of CPS/IoTs, as we need to adapt standards and best practice methods to include emerging new risks.

- Ensure dependability not only within the scope of an individual component, but also within the scope of the entire system.

- Re-evaluate the dependability model in use, and explore new properties, for example sustainability, which are becoming more important with the increase in connectivity and the quantity of computational units.

We will expand on these topics in Section 1.3 as we define specific research questions.

Why? In this section we argued for the necessity of dependable COS/IoT Ecosystems through examples and hinted to the gaps in the research on related topics.

#### 1.3 Aim of the Thesis

This thesis proposes a set of research questions highlighting CPS/IoT properties required for dependable operation. We emphasize individual research questions that identify roadblocks on this path, in addition to the state-of-the-art technologies that can be used to mitigate these challenges, and create emerging concepts. Together, they create a baseline for dependable design, development, and operation of CPS/IoT applications.

#### RQ1: How to build dependable hardware architectures for CPS/IoTs?

| Attributes        | $\mathbf{RQ1}$ | $\mathbf{RQ2}$ | RQ3          | $\mathbf{RQ4}$ | $\mathbf{RQ5}$ | $\mathbf{RQ6}$ | $\mathbf{RQ7}$ |

|-------------------|----------------|----------------|--------------|----------------|----------------|----------------|----------------|

| Testability       | $\checkmark$   |                | $\checkmark$ |                |                |                |                |

| Sustainabilty     | $\checkmark$   |                | $\checkmark$ |                | $\checkmark$   |                | $\checkmark$   |

| Performability    |                | $\checkmark$   |              |                |                | $\checkmark$   |                |

| Explainability    | $\checkmark$   |                | $\checkmark$ |                | $\checkmark$   | $\checkmark$   | $\checkmark$   |

| Scalability       |                | $\checkmark$   | $\checkmark$ |                | $\checkmark$   |                |                |

| Reconfigurability |                |                |              |                | $\checkmark$   | $\checkmark$   |                |

| Availability      | $\checkmark$   | $\checkmark$   | $\checkmark$ |                |                | $\checkmark$   | $\checkmark$   |

| Reliability       | $\checkmark$   |                | $\checkmark$ | $\checkmark$   |                | $\checkmark$   |                |

| Safety            | $\checkmark$   |                | $\checkmark$ | $\checkmark$   |                | $\checkmark$   |                |

| Confidentiality   |                |                |              | $\checkmark$   |                | $\checkmark$   |                |

| Integrity         |                |                |              | $\checkmark$   | $\checkmark$   | $\checkmark$   |                |

| Maintainability   |                |                |              |                | $\checkmark$   | $\checkmark$   | $\checkmark$   |

Table 1.1: Mapping research questions to dependability attributes.

Multi-core commercial off-the-shelf (COTS) processors are designed for optimal performance in systems with no critical consequences (s.a., death, economic loss) in case of failure. Primitive non-deterministic scheduling and other similar features make the multicore architectures not viable for safety-critical applications, if used in high-performance multi-core modes of operation. Ensuring dependable execution while maintaining acceptable performance capabilities is a rather difficult challenge.

#### RQ2: How to achieve virtualization of hardware resources in time?

A deterministic multi-core processor architecture has limited interface access due to safety and security requirements. Thus, individual cores may run into race conditions for hardware resources if not clearly divided between individual cores.

## **RQ3:** How to enable dependable mixed-criticality integration in many-core architectures?

Deterministic multi-core systems provide excellent conditions for safety constrained systems. However, state-of-the-art safety constrained systems are increasingly more entangled with non-critical systems. The non-critical systems commonly require higher performance factors, and they communicate with safety components.

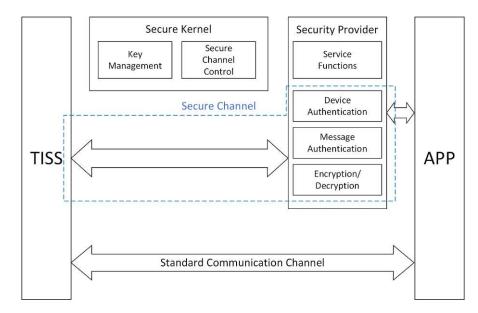

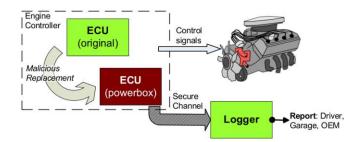

## **RQ4:** How to achieve a transparent and secure communication architecture on integrated MPSoC?

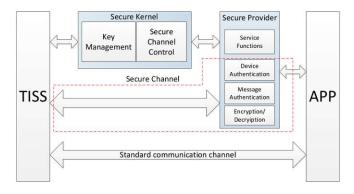

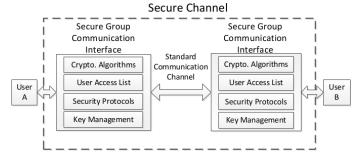

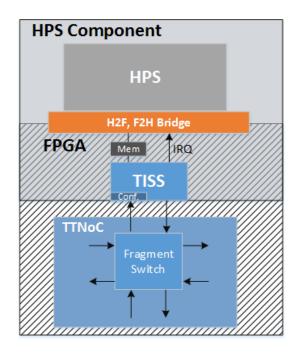

Deterministic MPSoCs are built upon the notion of strictly isolated components, including processing and network components. This baseline can be used to achieve secure communication both on and off the chip with little to no overhead on application nodes. We propose a secure channel architecture where secure information is completely hidden from the application cores, and all security services are offered by a trusted secure core.

#### RQ5: How to conceptualize synergies between CPS and IoT?

CPS is a computational system that interacts closely with the physical world either through perception or manipulation. A CPS is commonly represented by a control loop monitoring a physical system; based on the model of that system, it creates decisions that control it. IoT is a networking concept that creates a link between CPSs independent of its size or function. These systems are composed together in systemof-systems overlapping computing and communication infrastructure. This results in a highly-complex structure of heterogeneous devices and software components, that is progressively harder to interpret, grasp and analyze. The question that arises is how can we hierarchically structure CPS/IoTs in a way we can understand this composition to the point that it can be used in applications requiring a high level of confidence?

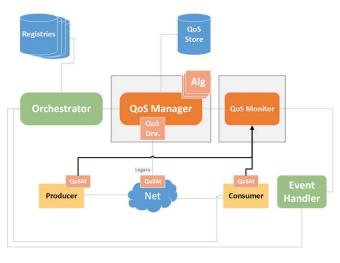

#### RQ6: How to ensure QoS through run-time verification and monitoring on the entire scale of operation of a CPS/IoT Ecosystem?

As the system gets more complex we need to apply automation and reduce manual effort in development and maintenance, in order to avoid faults caused by human error or process desynchronization. This would increase the overall ability to keep a system stable for a longer periods, and significantly reduce downtime. How can we increase QoS by reducing manual effort in development and using exiting infrastructure supporting run-time verification methods onto these processes?

#### **RQ7:** How to achieve sustainable CPS/IoT Ecosystems?

The energy component is a significant cost overhead in industrial production. The introduction of swarm-like systems with billions of devices makes this cost overhead to an important and ubiquitous problem for the industry. Reducing the energy footprint of computational devices would increase their overall dependability as they would ultimately be less of a liability economically and environmentally speaking.

#### 1.4 **Publications**

In order to give an overview of the publications relevant to this thesis we list them and provide a short name that will be used in the remainder of this document as a reference. We also provide a short discussion about the author's contributions to the individual papers. Publications marked with \* are included in the thesis.

- I (ACROSS MPSoC) The ACROSS MPSoC A New Generation of Multi-Core Processors designed for Safety-Critical Embedded Systems / C. El Salloum, M. Elshuber, O. Höftberger, H. Isakovic, A. Wasicek, Talk: DSD 2012 (Euromicro Conference on Digital System Design), Cesme, Izmir, Turkey (invited); 2012-09-05 - 2012-09-08; in: "2012 15th Euromicro Conference on Digital System Design (DSD 2012), Proceedings", IEEE Computer Society, (2012), ISBN: 978-1-4673-2498-4; 105 - 113 [88].

- II (ACROSS MPSoC (Jurnal)) The ACROSS MPSoC A new generation of multi-core processors designed for safety-critical embedded systems, C. El Sal-

loum, M. Elshuber, O. Höftberger, H. Isakovic, A. Wasicek, Microprocessors and Microsystems, 37 (2013), 8, Part C; 1020 - 1032 [47].

- III-\* (Secure Channels) Secure Channels in an Integrated MPSoC Architecture / H. Isakovic, A. Wasicek / Talk: 39th Annual Conference of the IEEE Industrial Electronics Society, Wien; 2013-11-10 - 2013-11-13; in: "Industrial Electronics Society, IECON 2013 - 39th Annual Conference of the IEEE", (2013), ISSN: 1553-572x; 4488 - 4493 [67].

- IV-\* (Virtual CAN) Virtual CAN Lines in an Integrated MPSoC Architecture, A. Wasicek, O. Höftberger, M. Elshuber, H. Isakovic, A Fleck, Talk: 17th IEEE International Symposium on Object/Component-Oriented Real-Time Distributed Computing (ISORC), Reno, Nevada, USA; 2014-06-08 2014-06-12; in: "Proc. of the 12th IEEE International Conference on Industrial Informatics", (2014), ISSN: 1555-0885; 158 165 [93].

- V-\* (Hybrid MPSoC) A heterogeneous time-triggered architecture on a hybrid systemon-a-chip platform / H. Isakovic, R. Grosu, Talk: 2016 IEEE 25th International Symposium on Industrial Electronics (ISIE), Santa Clara, CA, USA; 2016-06-08

2016-06-10; in: "IEEE 25th International Symposium on Industrial Electronics (ISIE)", IEEE, (2016), ISSN: 2163-5145; 244 - 253 [63].

- VI (EMC<sup>2</sup> Project) The EMC2 Project on Embedded Microcontrollers: Technical Progress after Two Years / W. Weber, A. Hoess, J. van Deventer, F. Oppenheimer, R. Ernst, A. Kostrzewa, P. Doré, T. Goubier, H. Isakovic, N. Druml, E. Wuchner, D. Schneider, E. Schoitsch, E. Armengaud, T. Söderqvist, M. Traversone, S. Uhrig, J.C. Pérez-Cortés, S. Saez, J. Kuusela, M. van Helvoort, X. Cai, B. Nordmoen, G.Y. Paulsen, H.P. Dahle, M. Geissel, J. Salecker, P. Tummeltshammer. 2016 Euromicro Conference on Digital System Design (DSD), 2016, pp. 524-531, doi: 10.1109/DSD.2016.72. [94].

- VII-\* (Mixed-Criticality) A Mixed-Criticality Integration in Cyber-Physical Systems: A Heterogeneous Time-Triggered Architecture on a Hybrid SoC Platform / H. Isakovic, R. Grosu / in: "Solutions for Cyber-Physical Systems Ubiquity", 1; issued by: IGI Global; IGI Global, Hershey PA, USA 17033, 2018, (invited), ISBN: 9781522528456, 169 - 194 [64]

- VIII (HW for Safety) A Survey of Hardware Technologies for Mixed-Critical Integration Explored in the Project EMC2 / H. Isakovic, R. Grosu, D. Ratasich, J. Kadlec, Z. Pohl, S. Kerrison, K. Georgiou, N. Druml, L. Tadros, F. Christiansen, E. Wheatley, B. Farkas, R. Meyer, M. Berekovic / Talk: SAFECOMP 2017 DECSoS, Trento (invited); 2017-09-12 - 2017-09-15; in: "Computer Safety, Reliability, and Security", Lecture Notes in Computer Science / Springer, Volume 10486 (2017), ISBN: 978-3-319-66284-8; 124 - 140 [65].

- IX (Self-Healing) A Self-Healing Framework for Building Resilient Cyber-Physical Systems / D. Ratasich, O. Höftberger, H. Isakovic, M. Shafique, R. Grosu / Talk: 20th IEEE International Symposium on Real-Time Computing (ISORC 2017), Toronto, Canada; 2017-05-16 - 2017-05-18; in: "Real-Time Distributed Computing (ISORC), 2017 IEEE 20th International Symposium on", IEEE, (2017), ISBN: 978-1-5386-1574-4; 133 - 140 [86].

- X-\* (CPS/IoT Ecosystem) CPS/IoT Ecosystem: A Platform for Research and Education / H. Isakovic, D. Ratasich, C. Hirsch, M. Platzer, B. Wally, T. Rausch, D. Nickovic, W. Krenn, G. Kappel, S. Dustdar, R. Grosu / Talk: 14th Workshop on Embedded and Cyber-Physical Systems Education (WESE 2018), Turin, Italien; 2018-10-04 - 2018-10-05; in: "Cyber Physical Systems. Model-Based Design. 8th International Workshop on Model-Based Design of Cyber Physical Systems (CyPhy 2018), and 14th International Workshop on Embedded and Cyber-Physical Systems Education (WESE 2018)", R. Chamberlain, W. Taha, M. Törngren (ed.); Springer International Publishing, (2019), ISBN: 978-3-030-23702-8 [66].

- XI (Simulation for IoT) Sensyml: Simulation Environment for large-scale IoT Applications / H. Isakovic, R. Grosu, B. Wally, T. Rausch, S. Dustdar, G. Kappel, D. Ratasich, V. Bisanovic / Talk: 45th Annual Conference of the IEEE Industrial Electronics Society (IECON 2019), Lisbon, Portugal, Portugal; 2019-10-14 - 2019-10-18; in: "IECON 2019 - 45th Annual Conference of the IEEE Industrial Electronics Society", IEEE Xplore, (2019), ISBN: 978-1-7281-4878-6; 3024 - 3030 [54].

- XII (Smart Farming) CPS/IoT Ecosystem: Indoor Vertical Farming System, H. Isakovic, R. Grosu, A. Fasching, L. Punzenberger / Talk: 2019 IEEE 23rd International Symposium on Consumer Technologies (ISCT), Ancona, Italien; 2019-06-19 2019-06-21; in: "2019 IEEE 23rd International Symposium on Consumer Technologies (ISCT)", IEEE Xplore, (2019), ISSN: 0747-668x; 47 52 [55].

- XIII-\* (QoS for IoT) QoS for Dynamic Deployment of IoT Services, H.Isakovic, L.L. Ferreira, Irmin Okic, A. Dukkon, and R. Grosu, IEEE 22. International Conference on Industrial Technology ICIT 2021, Valencia, Spain [56].

- XIV-\* (Sustainable IoT) An Energy Sustainable CPS/IoT Ecosystem, H. Isakovic, E.A. Crespo and R. Grosu,(2021), EAI Edge-IoT 2020, In Paiva S., Lopes S.I., Zitouni R., Gupta N., Lopes S.F., Yonezawa T. (eds) Science and Technologies for Smart Cities. SmartCity360° 2020. Lecture Notes of the Institute for Computer Sciences, Social Informatics and Telecommunications Engineering. [61].

- XV (Adaptive Filters) Adaptive Signal Filtering Platform for a CPS/IoT Ecosystem, H. Isakovic, S. Dangl, Z. Tucakovic, R. Grosu, Special Session on the IEEE 22. International Conference on Industrial Technology ICIT 2021, Valencia, Spain [62].

#### 1.5 Methodology

In the scope of this thesis we will elaborate the main methods for achieving dependable CPS/IoT Ecosystems, provide an extensive overview of the state-of-the-art of scientific and industrial literature, and highlight the importance of our research and relevant publications towards this goal.

The previous sections introduced CPS/IoT Ecosystems as complex hierarchical structures establishing basic causal relations among its structural subunits. Individual components in CPS/IoT Ecosystems are designed and implemented as independent units. Their functions have causal effects on the other components and their basic properties. The notion of CPS/IoT Ecosystem follows the definition of CPSoS as mentioned earlier; however, it expands the typical CPSoS definition further from the perspective of uncertainty and entanglement between components with higher requirements on functional safety and components with low or no-requirements for functional safety.

#### 1.5.1 General Requirements

In order to understand the requirements behind dependable CPS/IoT Ecosystems, it is necessary to explain the recent history in the development of cyber-physical systems applied in manufacturing, automotive and other industrial sectors with strict functional rules and regulations. Initiatives such as Industry4.0 [8] from the German public and industrial authorities proposed radical revolution of industrial manufacturing systems towards functionally smarter and more efficient systems.

This revolution of industrial systems is supposed to create new values, business models, and improve overall social and economic benefits [69]. Another example where the industrial evolution is pushing the boundaries of technological and scientific development of cyber-physical systems is coming from the automotive industry. In particular, the introduction of autonomous and smart driving creates major challenges and yields extensive changes in the way how cars and their computer systems are implemented.

These new applications require that we transfer progressively more safety functions to fully automated systems (e.g., lane keeping, adaptive braking). They also require us to continuously increase the number of interconnections between local components and the outside world. For example, in the factory we are connecting in-factory systems with external software such as resource planning, accounting, and data analysis. The vehicles are connected to the surrounding infrastructure, or they are using the connection to the internet or smartphones to implement a smart in-vehicle instrumentation.

In order to achieve all these new features, systems need to be augmented by increasing connectivity, interoperability, and ubiquity while maintaining functional safety, security, and resource efficiency. To achieve the goals of Industry40, smart industrial systems must not only reach new levels of functional intelligence, but also improve on standardization and create new reference architectures, complexity management, and integration with other fields of operation such as supply chains, work organization and training, and regu-

latory supervision. Such systems must also increase overall connectivity by establishing broadband infrastructure for industry [69].

The evolution of cyber-physical systems and their ambient applications yields new technologies, methods and tools, under standardized guidelines and regulations. These systems were defined by properties and requirements proposed in the traditional dependability model [28]. However, new features and functions are producing emerging properties that are giving us a more enhanced description of the system.

What? The society constantly imposes new requirements on industrial systems; these trends are also reflected in computer systems. The computer systems need to be designed in a way that allows them to be easily adapted or upgraded to meet emerging needs of industry and society.

#### Architectural Significant Requirements (ASR)

The success of a system is pre-conditioned with the requirements that describe its function, behavior, and relations to other systems. The requirements that determine and shape the architecture of the systems can be defined as architectural significant requirements (ASR) [41]. In Section 1.2 we introduced a standard dependability model extended with additional attributes that emerged over time and that influence the systems ability to ensure a dependable operation.

In the scope of our work we observed emerging system properties that are going beyond the traditional dependability model and are vital for a dependable CPS/IoT Ecosystem:

- Mixed-criticallity the ability of the system to combine functionalities with high importance ("critical") for the correct operation of the system with others that might not be directly connected to the system's safe operation [33]. For example, to allow smart in-vehicle instrumentation that can manage both safety-critical functions and non-critical functions it is necessary to enable novel hardware architectures capable of separating these functions in space and time, in order to reduce possible interference to an absolute minimum [47].

- Virtualization is another property that is not included in the traditional model of computer-system dependability [28]. However, it is essential for most state-of-the-art computer systems. It is the function that allows a system "to divide resources on multiple execution environments, using one or more concepts or technologies" [81][91]. Use of virtualization as a means for achieving spatial isolation between components is an essential requirement in safety- and security-constrained systems.

- Quality-of-Service (QoS) stems from the communication aspect of computer systems, and it originally referred to the ability of the network to provide a service under specified requirements [42]. It is regulating a collection of properties such as throughput, latency, jitter, etc. The concept extended further in application design, and it became exclusively prominent in Internet applications, such as multimedia

14

streaming [25]. Industrial applications and the applications with safety constraints such as automotive, are strictly defined by their specifications. The satisfaction of these conditions is determining their QoS level. This is a collection of requirements from communication, hardware behaviour, energy consumption, software execution matrices, and resource management. A QoS management component or service is an essential part of any state-of-the-art industrial software framework [26].

- Sustainability is a property that surpasses its definition as a technical requirement. Moreover, it can be observed as a global socio-economic challenge [36]. We can observe sustainability from multiple aspects, such as: a) technical or longevity of the system; b) environmental or impact of on a surrounding ecosystem; c) economic or ability to maintain positive financial balance; d) individual or the ability of an entity to progress and develop in an environment; e) and social that propagates communication between individuals and organizations and their ability to resolve conflicts potential disputes [35]. In the scope of CPS/IoT Ecosystem it is necessary to reflect on two requirements, reducing power consumption and increasing the operational lifespan of each device, software or system in general.

- Security is not a novel or emerging property in terms of definition and function. It is included in traditional dependability [28]. Moreover, it is one of the properties with a largest set of requirements and highest rate of change. In the scope of a CPS/IoT Ecosystem where we have a high number of heterogeneous devices, software components and communication protocols it is extremely difficult to envision a unified solution satisfying all security requirements [59]. There are two main aspects when observing security in CPS/IoT Ecosystem. The first is local, where we need to establish cyber-resilience of each individual component [77]. The second aspect is global, where we need to ensure security frameworks for secure design and implementation of CPS/IoTs [29]. In conclusion we state that a secure design process starts with a secure design of hardware devices and ends with the security-proofing the application, both from cyber and physical aspect.

**What?** We identified the above-defined properties as essential to achieve certain aspects of dependability in a CPS/IoT Ecosystem.

#### Quality Assurance and Standardization

Standards are means of regulation compiled in a document and approved by authorized experts as a rule or guideline to establish a certain level of quality, order, or functionality for an entity or organization in a given context [27]. Standards provide three types of information: a) Normative, or prescriptive measures one needs to take to conform to a standard, b) Informative, or descriptive knowledge that supports conceptual understanding of the topic, and c) Requirement, which are the criteria needed to satisfactorily comply with a standard [6].

Figure 1.5: The extended model for dependability with emerging properties.

Standards are characterized depending on the domain of application, intended use, and geographical and social circumstances. International standardization bodies that are relevant to CPS/IoT Ecosystems are:

- International Electrotechnical Commission (IEC) [9],

- International Organization for Standardization (ISO) [10],

- International Telecommunication Union (ITU) [11],

- Institute of Electrical and Electronics Engineers (IEEE) [19],

- Association Connecting Electronics Industries (IPC) [23],

- International Society of Automotive Engineers (SAE) [17], and

- World Wide Web Consortium [21].

These organizations provide regulations and guidelines for electronic systems, telecommunication and computer systems on a global scale. Different regions or countries will have their respective standardization bodies e.g., National Institute of Standards and Technology (NIST) [13] or European Telecommunications Standards Institute (ETSI) [6] where standards can somewhat differ from international norms.

Standards relevant to CPS/IoT Ecosystems are mainly inherited from other domains. A major component are systems for embedded systems and development. Further, they are strongly influenced by the application domain where they are deployed, especially regarding the safety aspect. Table 1.2 shows a collection of standards that in one way or another support dependable design and implementation of CPS/IoT.

There is an ongoing initiative to standardize IoT in particular, with three standards that would regulate dependability norms, guidelines, and requirements for IoT systems. The standard marked as IEEE P2413 [7] is dealing with architectural frameworks for IoT. Further, the standard IEEE P1451 [14] works on the harmonization of IoT devices and

Figure 1.6: The mapping of the publications included in the thesis to the basic dependability attributes.

systems. The standard under designation IEEE P2510 [15] is providing guidelines for establishing quality of data sensor parameters.

In addition to IEEE standards for IoT, there are other activities that are working on regulating CPS/IoT such as the Framework for Cyber-Physical Systems published by NIST [53], or IoT-Enabled Smart City Framework by IES [38].

All these initiatives are working towards a common goal, which is to establish a standardized basis for dependable design and implementation of CPS and IoT applications, which we characterize as CPS/IoT Ecosystem.

What? Standards provide us with normative, guidelines and requirements that if applied will produce a guarantee of achieving certain properties. We are aiming towards CPS/IoT Ecosystems that are conform with standards.

| Organization | Standard               | Domain                     | Topic                                      |  |  |

|--------------|------------------------|----------------------------|--------------------------------------------|--|--|

| ISO/IEC      | 29164                  | Biometrics                 | Embedded Framework                         |  |  |

| ISO/IEC      | 25000:2005             | Software Engineering       | Software Quality                           |  |  |

| ,            |                        | Software Engineering       | Requirements and Evaluation                |  |  |

| ISO/IEC      | 9496                   | Embedded Systems           | CHILL Language                             |  |  |

| ISO/IEC      | 18372                  | Hardware Design            | RapidIO Chip Interconects                  |  |  |

| ISO/IEC      | 62061                  | Industrial machines        | Safety Machinery                           |  |  |

| ISO/IEC      | 26262                  | Automotive                 | Safety                                     |  |  |

| ISO/IEC      | 9126                   | Software Engineering       | Software Quality                           |  |  |

| IPC          | 6011-6018              | Circuit Boards             | Quality of PCBs                            |  |  |

| IPC          | 9151                   | Circuit Boards             | Process Quality                            |  |  |

| IPC          | 9194, 9199             | Circuit Boards             | Statistical Process Control (SPC)          |  |  |

| IPC          | 4811, 4821, 2316, 7091 | Embedded Systems           | Design and production                      |  |  |

| IFU          | 4011, 4021, 2010, 7091 | Embedded Systems           | guidelines for embedded PCB                |  |  |

| IPC          | 7090-7095              | Embedded Systems           | PCB Packaging                              |  |  |

|              |                        |                            | Safety,                                    |  |  |

| IEC          | 61508,61511,61513      | Control systems            | Industrial Systems,                        |  |  |

|              |                        |                            | Nuclear Industry                           |  |  |

| IEC          | 62278                  | Railway                    | Safety                                     |  |  |

| IEC          | 62304                  | Medical                    | Safety                                     |  |  |

| IEEE/IEC     | 62014                  | System On Chip             | Quality of electronics and software        |  |  |

| IEEE         | 1500                   | Embedded Systems           | Testing and integration                    |  |  |

|              |                        |                            | Access and control                         |  |  |

| IEEE         | 1687                   | Embedded Systems           | for instrumentation in                     |  |  |

|              |                        |                            | semiconductor devices                      |  |  |

| IEEE         | 1003                   | Information Technology     | Operating System, Interfaces, Applications |  |  |

| IEEE         | 1450                   | Digital Design             | Testing Language                           |  |  |

| IEEE         | 802                    | Communication              | Protocols, interfaces,                     |  |  |

| IEEE         | 802                    | Communication              | synchronization                            |  |  |

| SEA          | J2356                  | Distributed Systems        | Model                                      |  |  |

| SEA          | J2640 Embedded Systems |                            | Software Design Automotive                 |  |  |

| SEA          | AS5506                 | Embedded Real-Time Systems | Architecture Analysis                      |  |  |

| SEA          |                        | Embedded Real-Time Systems | & Design Language (AADL)                   |  |  |

Table 1.2: International standards that support dependable CPS/IoT Ecosystem [27]

#### 1.5.2 Methods

The scientific method consists of a constant investigation of existing scientific theories and publishing of new theories [51]. It requires a continual assessment of testing methods and ongoing formulation of new tests that may provide additional insights on existing knowledge or create new knowledge [5]. In this work we adhered to this approach by starting our research with an evaluation of existing scientific works, creating a hypothetical baseline with applicable assumptions, creating experimental frameworks for testing and evaluation, and finally proposing new theories or augmenting existing ones.

Three predominant methodologies in computing research and related disciplines are: a) Theoretical methodology, which builds on mathematical foundations and explains the computing systems through logical reasoning and proofs; b) Experimental methodology, which relies on empirical evaluation of phenomena through series of tests and observations, c) Computer Simulation methodology, which studies phenomena by creating their respective computer models and simulating their behavior in various environments [51].

Works presented in Chapters 2-8, and other works presented in Section 1.4 are predomi-

Figure 1.7: An overview of research disciplines within CPSoS in relation to publications included in the thesis.

nantly accomplished by applying experimental methodology. However, as we can observe in Chapters 7, 8 or in publications [88], [47], [86] we combined theoretical methodology with experimental evaluations. In the work proposed in [54] we proposed a simulation environment that strongly supports a computer simulation methodology approach.

Further, we conducted a case study for CPS/IoT Ecosystem based on a real-world application [55]. In addition, we created a survey of innovative hardware technologies for mixed-criticality integration [65], including another important method of scientific research in our research background.

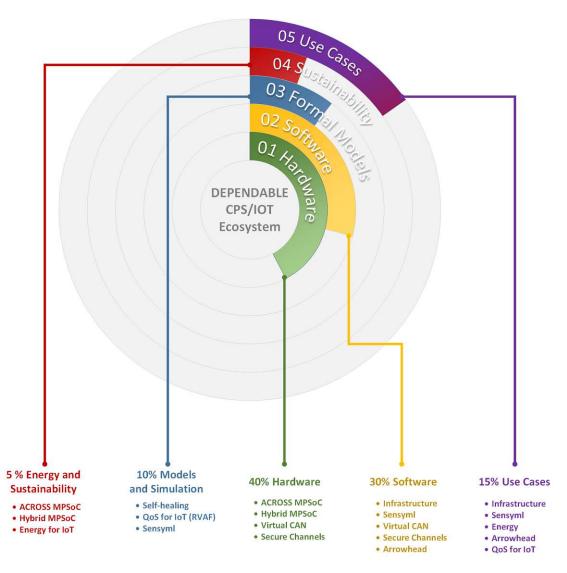

The work presented in this thesis covers five different fields of research within computer science (see Figure 1.7):

- Hardware focusing on research and development of hardware architectures or components, in the extent of 40% of published works.

- Software with a focus on development and evaluation of system software, middleware and applications, estimated to around of 30% work completed.

- Case Studies and Surveys transferring research ideas into real-world scenarios and collecting fundamental information on existing research and technologies as the basis for the works presented in our publications. We estimate the extent of this research at 15%.

- Models and Simulation creating relevant simulation frameworks for CPS/IoT Ecosystems and proposing relevant models to create predictions and assumptions. This covers about 10% of the presented works.

- Energy and Sustainability describes research on energy aware systems and methods for conservation of energy in computing systems. This topic is presented in 5% of the work completed.

Using a standardized methodology and scientific method provides us with generic guidelines on how to organize and execute a research task. However, it doesn't tell us which tools to use to achieve this goal. In the following section we will introduce the most important concepts, frameworks, and tool-sets used in the research for this thesis and their relation to the notion of dependable CPS/IoT Ecosystem.

**How?** In this section we identify methods that can be used to achieve above defined goals and requirements.

#### 1.5.3 Architectural Concepts and Frameworks

In the following section we will identify architectural concepts that are supporting the notion of dependable CPS/IoT Ecosystem. These systems are as mentioned before highly complex with an increasing trend, so they are built with a high grade of heterogeneity, both vertically across the operation layer spectrum (i.e., cloud, fog, sensor) and also horizontally within each operational layer. This is necessary to achieve the full system comprehension for a certain level of dependability. In the work presented in later chapters, we apply certain state-of-the-art concepts, tools, and methods that are designed to increase the degree of comprehension when building CPS/IoT Ecosystem.

How? In this section we specify architectural concepts, hardware and software frameworks to achieve dependable design, execution and operation of CPS/IoT Ecosystem.

#### Service-Oriented Architecture (SoA)

A Service-Oriented Architecture (SoA) approach comprises a system design and implementation with a focus on encapsulating functions in services which can be exchanged and applied over common interfaces [83]. An SoA approach supports extended dependability properties such as reconfigurability and interoperability, and can even be aligned with state-of-the-art standards for industrial automation (e.g., IEC 61499) [43]. Finally, an SoA approach is highly flexible, and we can design services from a hardware layer up to the application level as can be seen in the following two examples.

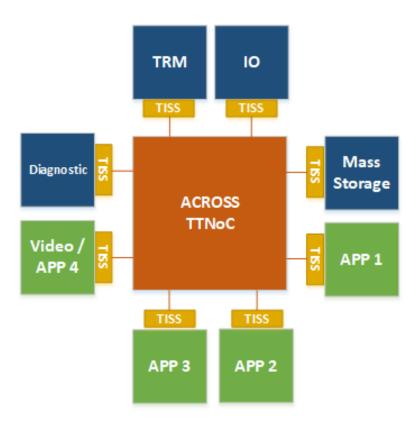

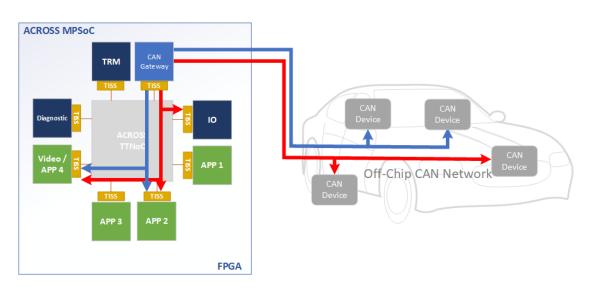

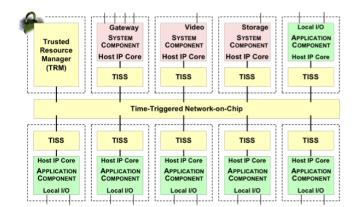

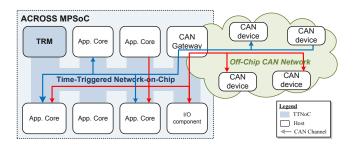

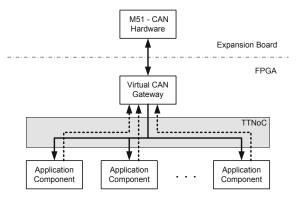

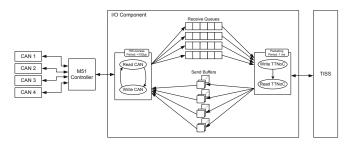

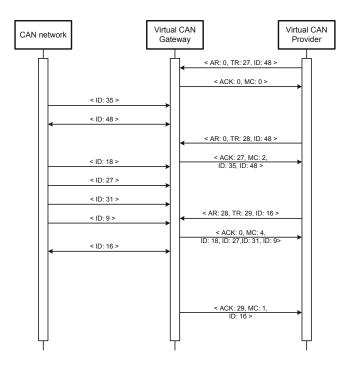

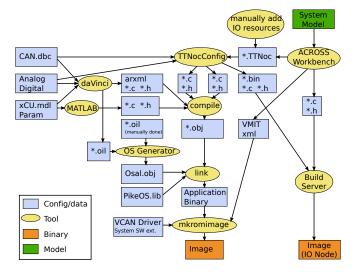

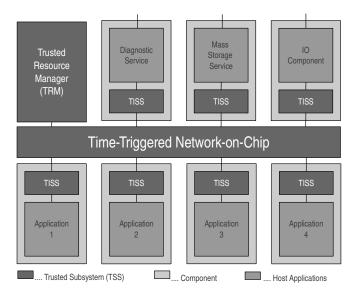

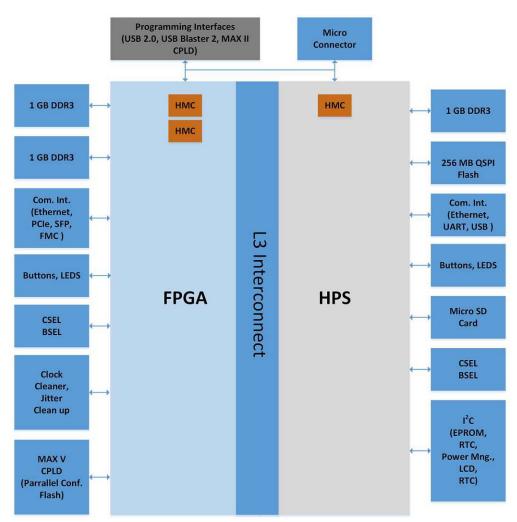

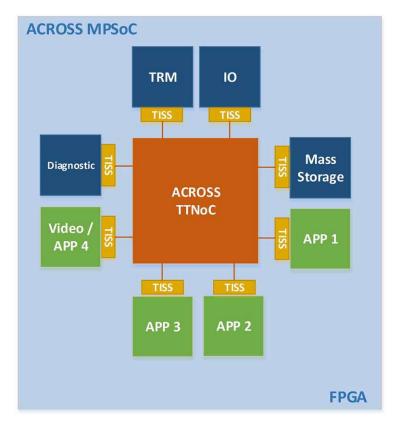

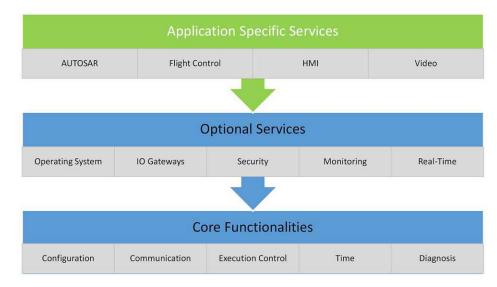

The work we present in Chapters 2, 4, 3, 5 is based on the ACROSS SoA multiple system on chip platform (MPSoC) [88], and earlier work on GENESYS architecture. [80]. They define a set of requirements for dependable distributed embedded systems which can be applied in multiple industrial domains. It propagates abstraction, partitioning, and segmentation as means of reducing complexity. An abstraction considers dividing the system into different integration levels: system, device, chip. A partitioning ensures strict separation between components on each level of abstraction, and a segmentation reduces task complexity by dividing a complex task in a series of simpler jobs. The services can be divided as: a) core services or essential services, b) optional services or system functions that are not essential in every instance, c) application-specific services. The perspective of the system services can be local and confined to a single component, or global and available to the whole ensemble.

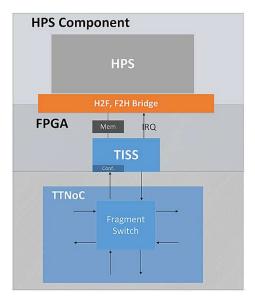

Furthermore, the work presented in Chapter 7 is implemented using the Arrowhead framework [46]. The Arrowhead framework is designed for automation of IoT systems and their secure and dependable application in industrial systems. It is conceptualized on the notion of local clouds. Applications and systems are automated using a multi-cloud approach, where each cloud maintains a set of services that can be operated locally or exchanged with other clouds using a secure connection. Each cloud is designed around a set of core mandatory services and application-specific services.

A CPS/IoT Ecosystem is a heterogeneous and complex structure. In order to apply it in systems with strict safety and security constraints we need to increase the explainability of the system and ensure temporal and spatial isolation of components. Use of standardized interfaces as a binding element reduces complexity and provides composability, the ability to add and remove components without custom integration requirements [80].

**How?** We used SoA architectures to create a basic environment for dependable CPS/IoT Ecosystem. It is an important part for answering Research-questions RQ1 - RQ6.

#### Hardware Acceleration and MPSoC

A common approach to building cyber-physical systems (CPSs) is a homogeneous hardware platform either with software running on COTS hardware or custom-built dedicated hardware. However, in recent years the trends are evolving towards more heterogeneous and more flexible solutions. This revolution is driven by two major paradigm shifts: a) Building CPS as a single multidisciplinary process rather than an ambiguous set of independently created systems, and b) Internet-of-Things (IoT), an enormous collection of independent systems operating in isolation or in groups over the internet.

Major challenges behind these paradigm shifts include: "retirement" of single core chips, performance increase for rapid increase in additional functionality, reduction in size, energy consumption, and security. For years now single-core CPUs have been replaced by multi-core variants due to the obvious advantages of increased performance, reduced power consumption, etc. In consumer electronics this change has been adopted easily. However, in industrial applications, especially ones with safety related requirements, this change is much more challenging to implement. Certification of devices without clear separation between different operational units is an extremely difficult task.

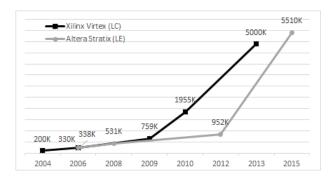

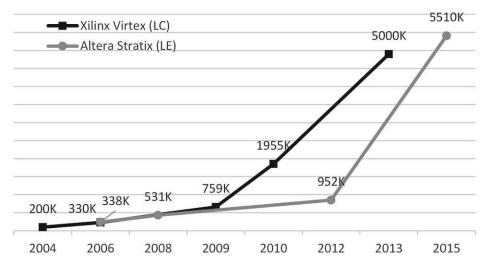

Field Programmable Gate Array (FPGA) platforms created a huge impact on server and data center technology already [85]. With hybrid SoC platforms the advantages of FPGA flexibility and performance can be also transferred in other applications ranging from small IoT devices (e.g. ZyngBerry [52]) to applications complex as Advanced Driver Assistance Systems (ADAS) [87][4].

Hardware accelerators are becoming a well-established tool in the scope of CPS/IoT Ecosystem due to their flexibility, and the ability to support both essential dependability requirements and the extended requirements that we defined in Section 1.5.1.

A System-on-chip represents a fully functional system that is contained within a single chip, including all of its core components: processor, memory, and peripherals on-board [50]. This means that we could have a full system working as hardware accelerators or components for dedicated tasks, or with a certain level of dependability.

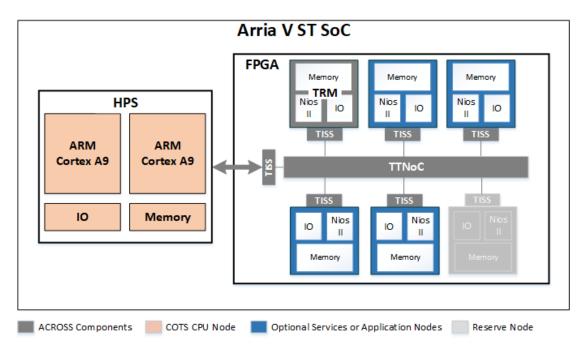

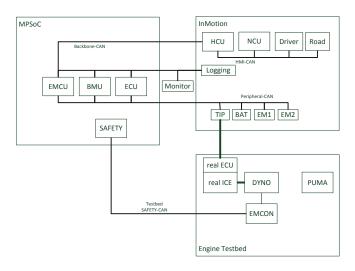

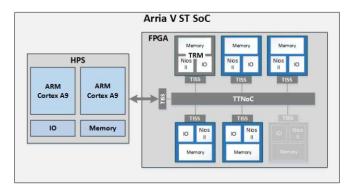

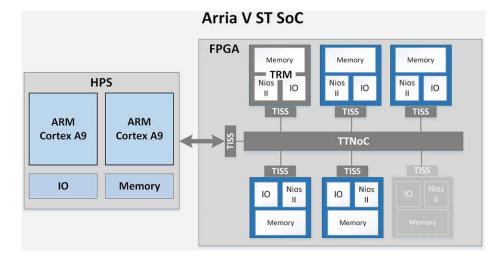

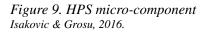

A hybrid multiple system-on-chip (MPSOC) approach can be observed in Chapters 4, 5, where we enable mixed-criticality integration through separation of functions. The safety functions were performed on an FPGA-based custom-built components, and non-critical functions on a loosely coupled COTS-based system (i.e., ARM).

Further, hardware accelerators can be also an efficient Fog device within a CPS/IoT Architecture, where it can be used as communication hub or data analysis system. We demonstrated how to implement FPGA based re-configurable nodes for adaptive signal processing using a similar approach [62]. Hardware accelerators are used from cloud servers, over network infrastructure, to data analysis in fog. In addition to clear performance advantages they also support energy-sustainable development with clear advantage over CPU or GPU solutions [74], [76].

How? We used hardware accelerators on an FPGA basis and MPSoCs as a platform for implementation of dependable hardware architectures. This is the cornerstone technology for Research-questions RQ1 - RQ4.

22

# Time-Triggered System-on-Chip (TTSoC) Architecture

Dependable systems include safety-critical systems, or systems where failure to properly function can result in catastrophic consequences. Safety-critical systems have strict deadlines for communication and execution of tasks [70]. The time-triggered architecture is a framework for the design and implementation of large dependable deterministic systems [71]. TTSoC represents a component methodology that integrates the design principles of an SoC with a deterministic time-triggered framework [82]. It allows the implementation of distributed systems in a fully deterministic way.

In our work on the ACROSS [47] architecture we demonstrated how a high level of temporal and spatial determinism can be achieved using a TTSoC enabling the integration of multiple safety critical systems or functions on a single chip. The temporal and spatial determinism can be also characterized as an essential feature when building mixed-criticality applications as described in Chapters 4 and 5.

Time-triggered architectures are designed for a high level of composability [71]. This is a property that enables systems to expand and compose into larger systems without any side effects [82]. This allows systems to expand, reduce, and reconfigure such that the eventual faults at the interfaces between individual components are contained.

The time-triggered paradigm is not exactly reserved for highly critical systems and applications. The IEEE 802 standard [12] is constantly expanding and introducing "time-triggered" features. This brings time-sensitive communication into the standard Ethernet communication infrastructure. This will provide a necessary determinism. This will reduce need for proprietary hardware or software and increase overall interoperability. In conclusion, the time-sensitive communication infrastructure is an essential component of a dependable CPS/IoT Ecosystem.

**How?** Certain types of systems require extreme determinism and the time-triggered communication architectures are designed to facilitate this kind of determinism. TTNoC is an on-chip communication technology that enables solutions for RQ1-RQ4.

# **Runtime Verification and Monitoring**

To establish the confidence in a computational system and increase its credibility, it is necessary to have a process of "checks and balances" in terms of scientific observation and evidence. Runtime Verification as a field of research stems from a discipline in computational science called Verification & Validation (V&V).

V&V are two essential processes when evaluating and quantifying the correctness of a computational artefact. [79]. Verification is "the process of assessing software correctness and numerical accuracy of the solution to a given mathematical model". Validation is "the process of assessing the physical accuracy of a mathematical model based on comparisons between computational results and experimental data" [79].

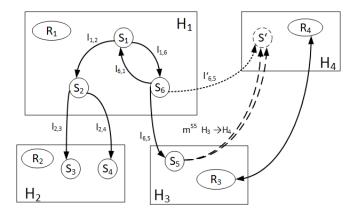

V&V methods observe the full spectrum of system executions and corresponding results. This is achieved by either watching the data generated by the solution of the associated models, or by watching and analysing the experimental results. Runtime Verification (RV) is a subset of V&V, that checks the results of the system's execution against the ones of the model's solution [32]. Sometimes it is referred to as Runtime Monitoring (RM).

RV can be applied to the verification of software components such as functions, services of full programs. Furthermore, it can be used to verify communication protocols and data flow. However, one can also apply the same techniques to verify behavior of full systems such as Fog nodes, industrial machines or vehicles.

CPSs are closely coupled with their respective physical surroundings and as such their execution can be unpredictable to some extent. It is often unfeasible to build a model that can perceive all possible scenarios. Likewise, it is difficult to collect the full spectrum of data necessary to verify all possible execution scenarios. RV provides an alternative approach whereby we observe and verify a single execution at a time, observing relevant variables and checking their correctness at simulation time or on runtime [30].

Information from RV can be used to detect and correct incorrect behavior of a system or its components as presented in [86]. Further, it is a mechanism that can provide guarantees to establish system attributes such as QoS and reach certain level of dependability as shown in Chapter 7.

**How?** The formal verification of a system is an essential component in its certification. Runtime Verification allows us to evaluate a working system and make sure that its operation is satisfying the system specification. With a high number of extremely heterogeneous components it is difficult to achieve formal verification off-line. Thus, we need to use an on-line verification framework for each individual component.

#### Dynamic Reconfiguration, Self-healing or Self-adaptation

The ability to tolerate faults and errors, and to resist external influences, is a crucial requirement for safety-critical systems and systems with higher functional constraints. A common approach to fault tolerance is to apply modular redundancy of critical components; this way if one component fails the redundant copies can proceed with the operation [70]. To increase the efficiency of the system one can apply reconfiguration methods that will restore the system or component in case of a fault or an error. Another way to establish fault tolerance is to use implicit redundancies within a system to perform system reconfiguration or adaptation.

In the work we presented in [86] we identified two types of self-healing: structural adaptation and parametric adaptation. In this work we elaborate on the advantages of structural adaptation where a function of a system is restored by rearranging the order of components to replace the faulty ones. In Chapter 7 we present strategies for system reconfiguration that can perform structural and parametric adaptation as well as the combination of two methods.

Self-healing in CPS/IoT Ecosystems provides the ability to tolerate faults without the need for explicit redundancies. The ability of the system to reconfigure and restore its

original function after a fault is an extended attribute of dependability. It also supports other attributes such as availability and sustainability.

**How?** A system's robustness is often determined by its design. In highly volatile and dynamic systems we are often faced with unpredictable situations that may or may not be defined in the initial design of the system. Thus, the system is not always capable of coping with the emerging faults. Having dynamic reconfiguration mechanisms allows us to adapt to unforeseen scenarios during runtime.

## Simulation

Simulation is one of three major research methodologies in computing research [51]. It is the process of understanding or evaluating a system through the observation of its model under the constraints of a simulated environment, where one can observe a system as a whole or as a collection of its components [90]. Computer simulation provides us with the ability to reproduce working conditions of even most complex physical systems in real-time [31]. Studies have shown that the Simulation and model representation of physical systems is one of the main pillars of Industry4.0 [95].

In the work we presented in [54] we demonstrate how simulation can be used to replace a large-scale application environment in CPS/IoT to evaluate among other attributes the scalability of a CPS/IoT Ecosystem implementation.

**How?** Simulation allows to explore the system dynamics at pre-design or at preimplementation time. This in turn allows engineers to create computer systems that are better suited for a specific physical system.

# Green Computing

Green Computing refers to the ecologically responsible use of computers and their resources, and the design and development of methods that reduce energy consumption and chemical footprint. It also provides guidelines on ecologically sensible disposal of old devices [20]. Green computing initiatives don't affect only consumption but also resource distribution, power management, organization, dimension, and other ways to reduce energy and waste overheads [92].

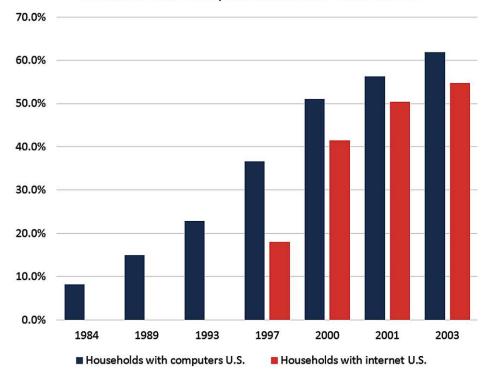

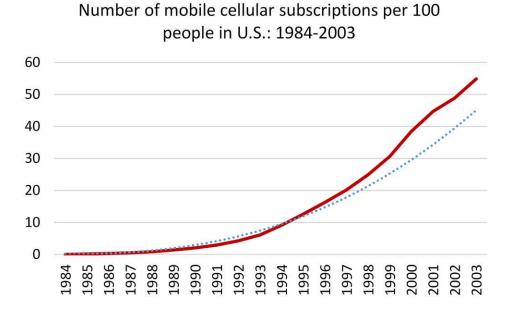

In Section 1 we presented the future trends in the expansion of CPS/IoT devices, with the tendency for the number of devices to reach 100 billion by 2030. This represents a major overhead on the electrical and environmental infrastructure. The devices used in a CPS/IoT Ecosystem should be therefore designed with a certain level of sustainability, which is not only represented in the energy consumption, but also in the longevity of the devices, and their ability to be serviced and maintained.

For example, the cryptocurrency surge in recent years created a cryptomining industry. The decentralized nature of these activities makes it incredibly difficult to track how much energy they are using. However, models show that the publicly accessible Proof-of-Work block-chains are consuming something in the range of 60 to 125 TWh of electrical energy

per year [89]. The use of energy-inefficient devices for cryptocalculations is creating a major global overhead both in energy consumption and in the population created by it. A similar scenario could be possible with CPS/IoT devices and smart applications if not approached systematically from the beginning.

Chapter 8 introduces an energy consumption model for CPS/IoT Ecosystems as defined in Chapter 6. In addition, we show how alternative design methods such as use of energy harvesting could reduce energy and chemical footprint in large CPS/IoT applications.

**How?** The rapid increase of computer systems is creating a growing energy and waste footprint in the world. Building energy-efficient and long-lasting computer systems is becoming a necessity, especially if we want to over-populate the world with computer systems creating the so called Smart World.

# Development and Operations (DevOps)

DevOps is a concept that bridges the gap between development and operation of software systems. It comprises the automated management of software development, integration, testing, deployment and delivery, monitoring and feedback [68]. It is a widely accepted practice in the world of software engineering, especially for web-based applications [34].

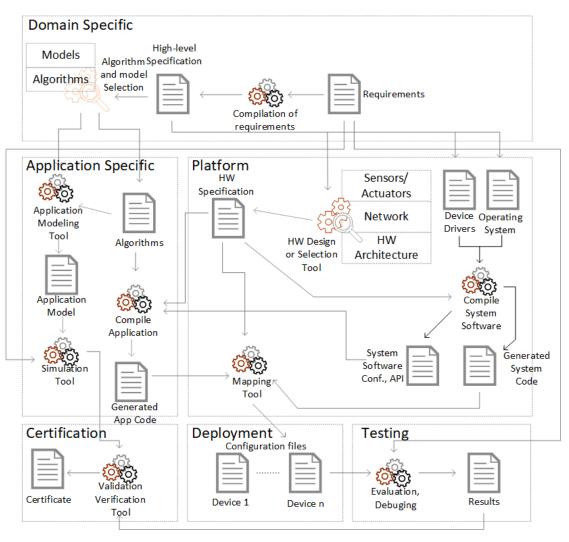

However, DevOps is a relatively new concept for CPS and IoT, where development processes are often ad-hoc and developer-centric. This approach is human-error prone, especially when it comes to integration in large and complex projects. The faults are readily propagated throughout the system, while debugging and testing is often extremely difficult to perform. We consider DevOps to be an essential requirement for CPS/IoT Ecosystems. It reduces development time and human-error potential, and also significantly decreases costs in development and operation.

**How?** If we look at any model for the development of computer systems or software, e.g., the V-model, we can observe that a major portion of the computer system's life-cycle is in design and development. For CPS/IoT Ecosystems this process is even more complex, as it potentially includes multiple sub-systems, components, and organizations. Having an automated process that supports design, development, testing, and monitoring is essential in order to cope with the complexity of these systems.

# 1.5.4 Evaluation of Dependability Properties

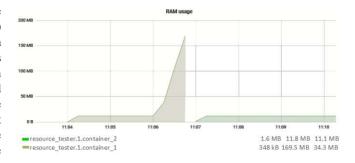

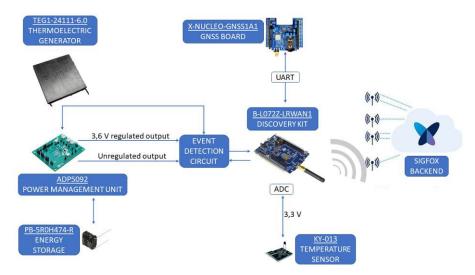

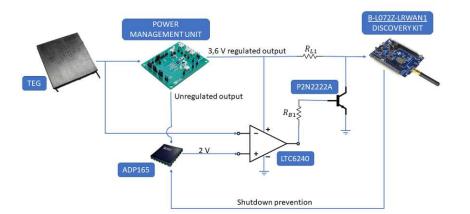

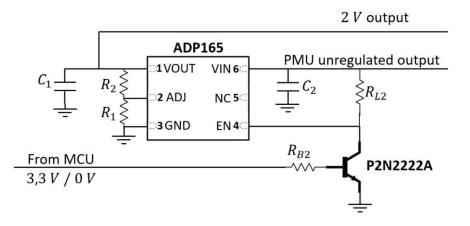

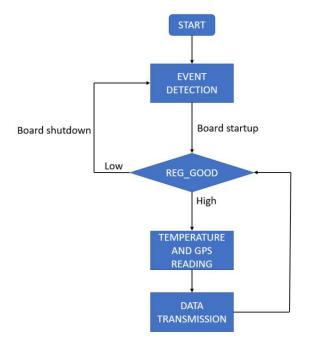

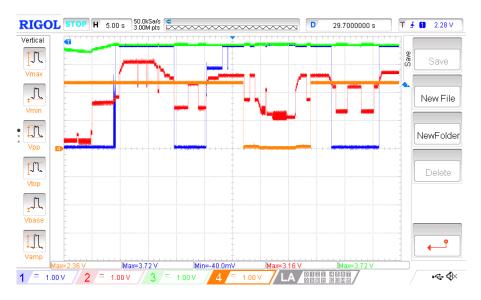

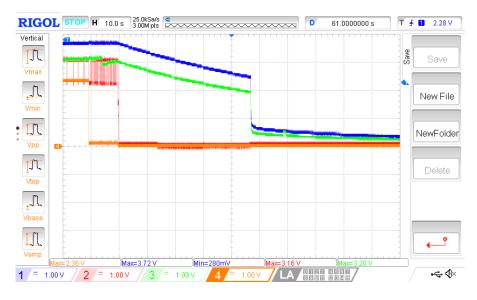

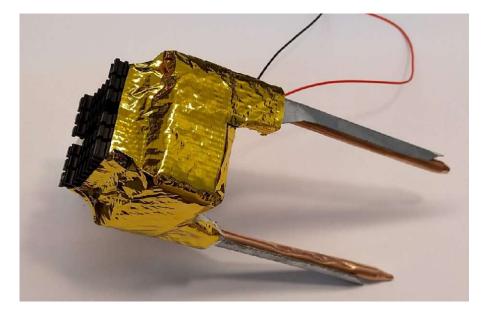

In previous section, we discussed architectural concepts and frameworks employed in later chapters in order to satisfy the requirements of Section 1.5.1. In Section 1.5.2 we indicated which basic methodologies were used in the scope of the research activities presented in Chapters 2-8. We concluded that the experimental methodology is the most often applied method to evaluate proposed theories and hypothesis.